Switching Characteristics#

For clock, reset and JTAG timing refer to the XU316-1024-QF60B datasheet. XVF3800 specific interface timings are detailed below.

QSPI Master (External flash for boot image storage)#

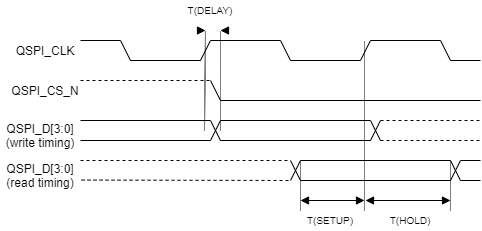

Fig. 7 QSPI Timing#

Parameter |

Symbol |

Min |

Typical |

Max |

Units |

|---|---|---|---|---|---|

QSPI Clock frequency |

f(QSPI_CLK) |

- |

12.5 |

MHz |

|

QSPI_CLK to QSPI Data output delay |

T(DELAY) |

-2.7 |

- |

2.7 |

ns |

QSPI Data input to QSPI_CLK Setup time |

T(SETUP) |

22 |

- |

- |

ns |

QSPI Data input to QSPI_CLK hold time |

T(HOLD) |

-11 |

- |

- |

ns |

I2S Slave#

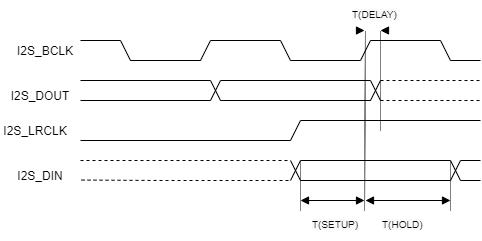

Fig. 8 I2S slave timing#

Parameter |

Symbol |

Min |

Typical |

Max |

Units |

Notes |

|---|---|---|---|---|---|---|

Master clock input frequency |

f(MCLKin) |

- |

24.576 |

- |

MHz |

A |

I2S Bit Clock frequency input |

f(I2S_BCLK) |

- |

1.024/3.072 |

- |

MHz |

|

I2S Data Input (LRCLK) to I2S_BCLK setup time |

T(SETUP) |

0 |

- |

- |

ns |

B |

I2S Data Input (LRCLK) to I2S_BCLK hold time |

T(HOLD) |

6 |

- |

- |

ns |

B |

I2S_BCLK to I2S Data output delay |

T(DELAY) |

11 |

- |

21.3 |

ns |

Note

SPI Slave (External processor boot)#

Parameter |

Symbol |

Min |

Typical |

Max |

Units |

Notes |

|---|---|---|---|---|---|---|

SPI Clock frequency |

f(SPI_CLK) |

- |

12.5 |

50 |

MHz |

|

SPI_CLK to MISO output delay |

T(DELAY) |

11 |

- |

21.3 |

ns |

|

SPI Master Output Slave Input (MOSI) to SPI_CLK Setup time |

T(SETUP) |

0 |

- |

- |

ns |

|

SPI Master Output Slave Input to (MOSI) SPI_CLK hold time |

T(HOLD) |

6 |

- |

- |

ns |

|

Note

A: Timing also applies to SPI Chip Select input (SPI_CS_N)