# The XMOS XS3 Architecture

Publication Date: 2024/10/6 Document Number: XM-014007-PS v2.0.0

#### IN THIS DOCUMENT

| 1  | Introduction                               |

|----|--------------------------------------------|

| 2  | Interconnect                               |

| 3  | Concurrent Threads                         |

| 4  | The XCORE Instruction Set                  |

| 5  | Instruction Issue and Execution            |

| 6  | Instruction Set Notation and Definitions   |

| 7  | Data Access                                |

| 8  | Expression Evaluation                      |

| 9  | Branching, Jumping and Calling             |

| 10 | Resources and the Thread Scheduler         |

| 11 | Concurrency and Thread Synchronisation     |

| 12 | Communication                              |

| 13 | Locks                                      |

| 14 | Timers                                     |

| 15 | Ports, Input and Output                    |

| 16 | Memory model                               |

| 17 | Events, Interrupts and Exceptions          |

| 18 | Initialisation and Debugging               |

| 19 | Specialised Instructions                   |

| 20 | Floating point arithmetic                  |

| 21 | Vector unit                                |

| 22 | XCore XS3 Instructions                     |

| 23 | XCore XS3 Instruction Format Specification |

| 24 | XCore XS3 Exceptions                       |

| 25 | XCore XS3 Lanes                            |

|    |                                            |

## **1** Introduction

xcore.ai products combine a number of XCORE processors, each with its own memory, on a single chip. The programmable processors are *general purpose* in the sense that they can execute languages such as C; they also have direct support for concurrent processing (multi-threading), communication and input-output. A high-performance *switch* supports communication between the processors, and inter-chip XLINKs are provided so that systems can easily be constructed from multiple chips.

xcore.ai products are intended to make it practical to use software to perform many functions which would normally be done by hardware; an important example is interfacing and input-output controllers.

xcore.ai products are based on the XS3 architecture. The XS3 architecture is a evolution of the XS2 architecture. The main differences with the XS2 architecture are:

- Vector operations (Vector unit).

- ▶ Floating point operations (*Floating point arithmetic*).

- External memory (External memory and Software defined memory).

There are also extra instructions for counting leading sign bits, and defining shift operations with negative values..

#### 2 Interconnect

The interconnect provides communication between all XCORES on the chip (or system if there is more than one chip). In conjunction with simple programs, it can also be used to

support access to the memory on any XCORE from any other XCORE, and to allow any XCORE to initiate programs on any other XCORE.

The interface between an XCORE and the interconnect is a group of XLINKs which carry *control tokens* and *data tokens*. The data tokens are simply bytes of data; the control tokens are as follows.

- Tokens 0-127 (Application tokens). These are intended for use by compilers or applications software to implement streamed, packetised and synchronised communications, to encode data-structures and to provide run-time type-checking of channel communications.

- ▶ Tokens 128-191 (*Special tokens*) are architecturally defined and may be interpreted by hardware or software. They are used to give standard encodings of common data types and structures.

- Tokens 192-223 (Privileged tokens) are architecturally defined and may be interpreted by hardware or privileged software. They are used to perform system functions including hardware resource sharing, control, monitoring and debugging. An attempt to transfer one of these tokens to or from unprivileged software will cause an exception.

- ▶ Tokens 224-255 (*Hardware tokens*) are only used by hardware; they control the physical operation of the link. An attempt to transfer one of these tokens using an output instruction will cause an exception.

Four links connect each XCORE directly to an on-chip switch which provides non-blocking communication between the XCOREs. The switch also provides off-chip XLINKs allowing multiple XS3, XS2, and XS1 chips to be combined in a system. The structure and performance of the XLINK connections in a system can be varied to meet the needs of applications.

The links between XCORES and switches and the XLINKs can be partitioned into independent networks. This can be used, for example, to provide independent networks carrying long and short messages or to provide independent networks for control and data messages.

Messages are routed to *channel-ends* on a specific processor through the XLINKs using a *message header* which contains the number of the destination chip, the number of the destination processor and the number of a destination channel-end within the processor. These can be encoded using either 24 bits (16 bits chip and processor address, 8 bits channel address) or 8 bits (3 bits chip and processor address, 5 bits channel address).

Each switch has a configurable identifier and can also be configured to route messages according to the first component of each message header. It compares this bit-by-bit with its own switch identifier; if all bits match it then uses the second component to route the message to the destination XCORE. If the bits do not match, then it uses the number of the first non-matching bit to select an outgoing direction. The direction of each XLINK is set when the switch is configured and it is possible for several XLINKs to share the same direction thereby providing several independent routes between two switches.

The header establishes a route through the interconnect and subsequent tokens will follow the same route until one of two special control tokens is sent: these are end-ofmessage (END) and pause (PAUSE).

#### 2.1 XLINK Ports

The ports used for inter-chip XLINK communication use a transition-based non returnto-zero signalling scheme. Bits are sent at a rate derived from the XS3 clock; this rate can be programmed to meet applications requirements.

The XLINKs can be switched between a fast, wide mode and a slower, serial mode. Two encoding schemes are used.

#### 2.2 Serial XLINK

The serial XLINK uses two data wires in each direction. A transition on Wire 1 represents a one bit and a transition on Wire 0 represents a zero bit. The first bit of a *control* token is a one; the first bit of a *data* token is a zero; the next 8 bits are the token value. The two signal wires are both at rest between tokens and the final bit of each token is chosen to return the non-zero signal wire to the rest state; one of the signal wires must be non-zero at this point as nine bits have been sent.

On the serial link, the END and PAUSE tokens are coded directly as application tokens 1 and 2.

The link also uses several hardware tokens. The credit tokens are transmitted by the receiver to control the flow of data; each CREDIT*n* token issues credit to the sender to allow it to send *n* tokens. The HELLO token solicits initial credits, setting up a half-duplex link. To bring up a link, both sides have to issue a HELLO, and both sides have to respond to the HELLO with a CREDIT*n* token.

| use      |

|----------|

| CREDIT8  |

| CREDIT64 |

| CREDIT16 |

| HELLO    |

|          |

#### 2.3 Fast XLINK

The fast XLINK uses 1-of-5 codes with five data wires in each direction; a *symbol* is transmitted by changing the state of one of the wires. Each symbol has the following meaning:

| symbol         | meaning  |

|----------------|----------|

| Wire 0 changes | value 00 |

| Wire 1 changes | value 01 |

| Wire 2 changes | value 10 |

| Wire 3 changes | value 11 |

| Wire 4 changes | escape   |

A sequence of four symbols are used to encode each token. In the following e is an escape and v is one of the values 00, 01, 10, 11.

| symbol sequence | use                       |

|-----------------|---------------------------|

| VVVV            | 256 data tokens           |

| evvv            | 64 control tokens 192-255 |

| vevv            | 64 control tokens 128-191 |

| vvev            | 64 control tokens 64-127  |

| vvve            | 64 control tokens 0-63    |

There are some additional codes in which more than one symbol is an escape. These are used to code certain control tokens.

| symbol sequence | use                         |

|-----------------|-----------------------------|

| e e v v         | END tokens                  |

| vvee            | PAUSE tokens                |

| evve            | NOP (return to zero) tokens |

| e 11 11 v       | NOP (return to zero) tokens |

| e 00 e 00       | CREDIT8                     |

| e 01 e 01       | CREDIT64                    |

| e 10 e 10       | HELLO                       |

| e 11 e 11       | CREDIT16                    |

Because each token contains four symbols, at the end of each token there are always an even number of signal wires in a non-zero state. To send an END or PAUSE, one of the END or PAUSE tokens is chosen to leave at most two signal wires in a non-zero state; this can be followed by a NOP token which is chosen to leave all of the signal wires in a zero state.

The encoding of the credit and reset tokens has been chosen so that the state of the signal wires after the token is the same as it was before the token.

## **3 Concurrent Threads**

A single XCore enables a number of tasks to execute concurrently in *threads*. Each thread executes a series of instructions that follow a conventional three register operand model. Threads have access to *resources* that enable a thread to interact with other threads or the outside world.

Each XCORE has hardware support for executing a number of concurrent threads. This includes:

- ▶ a set of registers for each thread.

- ▶ a thread scheduler which dynamically selects which thread to execute.

- ▶ a set of synchronisers to synchronise thread execution.

- ▶ a set of channels used for communication with other threads.

- ▶ a set of ports used for input and output.

- ▶ a set of timers to control real-time execution.

- a set of clock generators to enable synchronisation of the input-output with an external time domain.

- ▶ a set of hardware locks to enable low level locking

Instructions are provided to support initialisation, termination, starting, synchronising and stopping threads; also there are instructions to provide input-output and inter-thread communication.

The set of threads on each XCORE can be used:

- to implement input-output controllers executed concurrently with applications software.

- ▶ to allow communications or input-output to progress together with processing.

- ▶ to allow latency hiding in the interconnect by allowing some threads to continue whilst others are waiting for communication to or from remote XCOREs.

The instruction set includes instructions that enable the threads to communicate and perform input and output. These:

- provide event-driven communications and input-output with waiting threads automatically descheduled.

- support streamed, packetised or synchronised communication between threads anywhere in a system.

- enable the processor to idle with clocks disabled when all of its threads are waiting so as to save power.

- ▶ allow the interconnect to be pipelined and input-output to be buffered.

#### 4 The XCORE Instruction Set

The main features of the instruction set used by the XCORE processors are as follows.

- Short instructions are provided to allow efficient access to the stack and other data regions allocated by compilers; these also provide efficient branching and subroutine calling. The short instructions have been chosen on the basis of extensive evaluation to meet the needs of modern compilers.

- ▶ The memory is byte addressed; however all accesses must be aligned on natural boundaries so that, for example, the addresses used in 32-bit loads and stores must have the two least significant bits zero. The memory is little endian.

- The processor supports a number of threads each of which has its own set of registers. Some registers are used for specific purposes such as accessing the stack, the data region or large constants in a constant pool.

- Input and output instructions allow very fast communications between threads within an XCORE and between XCOREs. They also support high speed, low-latency, input and output. They are designed to support high-level concurrent programming techniques.

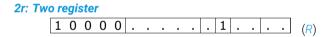

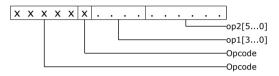

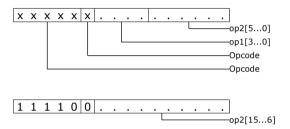

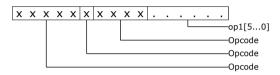

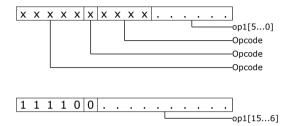

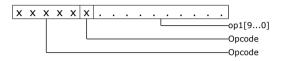

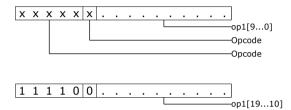

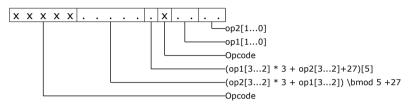

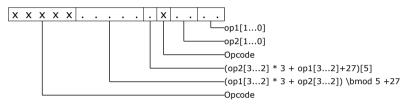

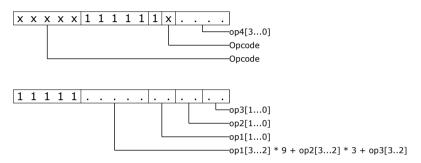

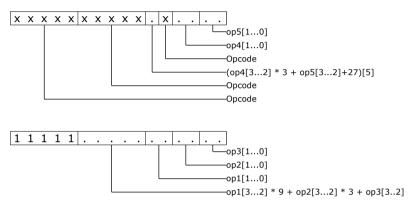

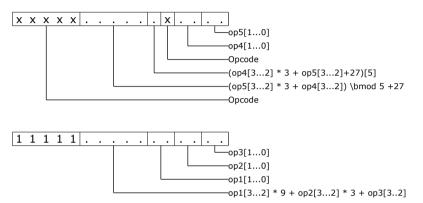

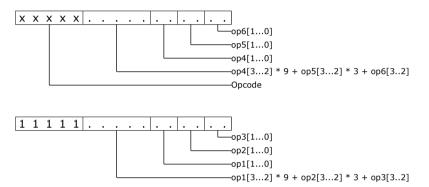

Most instructions are 16-bit. Many instructions use operands in the range  $0 \dots 11$  as this allows sufficient three-address instructions to be encoded using 16 bit instructions. Instruction prefixes are used to extend the range of immediate operands and to provide more inter-register operations (and inter-register operations with more operands). The prefixes are:

- PFIX which concatenates its 10-bit immediate with the immediate operand of the next 16-bit instruction.

- ▶ EOPR which concatenates its 11-bit operation set with the following instruction.

The prefixes are inserted automatically by compilers and assemblers.

The normal state of a thread is represented by 12 operand registers, 4 access registers and 2 control registers.

The twelve operand registers *r*0 ... *r*11 are used by instructions which perform arithmetic and logical operations, access data structures, and call subroutines.

The access registers are:

| register | number | use                   |

|----------|--------|-----------------------|

| ср       | 12     | constant pool pointer |

| dp       | 13     | data pointer          |

| sp       | 14     | stack pointer         |

| lr       | 15     | link register         |

The control registers are:

| register | number | use             |

|----------|--------|-----------------|

| рс       | 16     | program counter |

| sr       | 17     | status register |

Each thread has seven additional registers which have very specific uses:

| register | number | use                  |

|----------|--------|----------------------|

| spc      | 18     | saved pc             |

| ssr      | 19     | saved status         |

| et       | 20     | exception type       |

| ed       | 21     | exception data       |

| sed      | 22     | saved exception data |

| kep      | 23     | kernel entry pointer |

| ksp      | 24     | kernel stack pointer |

The status register *sr* contains the following information:

| bit      | number | use                                           |

|----------|--------|-----------------------------------------------|

| eeble    | 0      | event enable                                  |

| ieble    | 1      | interrupt enable                              |

| inenb    | 2      | thread is enabling events                     |

| inint    | 3      | thread is in interrupt mode                   |

| ink      | 4      | thread is in kernel mode                      |

| reserved | 5      | do not use                                    |

| waiting  | 6      | thread waiting to execute current instruction |

| fast     | 7      | thread enabled for fast input-output          |

| di       | 8      | thread is running in dual issue mode          |

| kedi     | 9      | thread switches to dual issue on kernel entry |

| hipri    | 10     | thread is in high priority mode               |

## 5 Instruction Issue and Execution

The processor is implemented using a short pipeline to maximise responsiveness. It is optimised to provide deterministic execution of multiple threads. There is no need for forwarding between pipeline stages and no need for speculative instruction issue and branch prediction. The memory is 128-bit wide, enabling sufficient instructions to be fetched simultaneously to enable the processor to run at full speed using a unified memory system. Long sequences of memory accesses require an occasional instruction fetch, consuming one extra thread cycle.

#### 5.1 Scheduler Implementation

The threads in an XCORE are intended to be used to perform several simultaneous realtime tasks such as input-output operations, so it is important that the performance of an individual thread can be guaranteed. The scheduling method used allows any number of threads to share a single unified memory system and input-output system whilst guaranteeing that with *n* threads able to execute, each will get at least 1/n processor cycles. In fact, it is useful to think of a *thread cycle* as being *n* processor cycles.

From a software design standpoint, this means that the minimum performance of a thread can be calculated by counting the number of concurrent threads at a specific point in the program. In practice, performance will almost always be higher than this because individual threads will sometimes be delayed waiting for input or output and their unused processor cycles can be taken by other threads. Further, the time taken to re-start a waiting thread is always at most one thread cycle. (Note that the use of priority threads will cause a slightly different but still predictable performance pattern, see *High priority threads*.)

The set of *n* threads can therefore be thought of as a set of virtual processors each with clock rate at least 1/n of the clock rate of the processor itself. The only exception to this is that if the number of threads is less than the pipeline depth *p*, the clock rate is at most 1/p.

Each thread has a 256-bit instruction buffer which is able to hold sixteen short instructions or eight long ones. Instructions are issued from the runnable threads in a roundrobin manner, ignoring threads which are not in use or are paused waiting for a synchronisation or input-output operation.

The pipeline has a memory access stage which is available to *all* instructions. The rules for performing an instruction fetch are as follows.

- Any instruction which requires data-access performs it during the memory access stage.

- Branch instructions fetch their branch target instructions during the memory access stage unless they also require a data access (in which case they will leave the instruction buffer empty).

- ▶ Conditional branches only ever fetch instructions around the target address.

- Any other instruction (such as ALU operations) uses the memory access stage to perform an instruction fetch. This is used to load the thread's own instruction buffer unless it is full.

- If the instruction buffer is empty when an instruction should be issued, a special fetch no-op is issued; this will use its memory access stage to load the issuing thread's instruction buffer.

There are very few situations in which a *fetch no-op* is needed, and these can often be avoided by simple instruction scheduling in compilers or assemblers. An obvious example is to break long sequences of loads or stores by interspersing ALU operations.

Certain instructions cause threads to become non-runnable because, for example, an input channel has no available data. When the data becomes available, the thread will continue from the point where it paused.

To achieve this, each thread has an individual ready request signal. The thread identifier is passed to the resource (port, channel, timer etc) and used by the resource to select the correct ready request signal. The assertion of this will cause the thread to be restarted, normally by re-entering it into the round-robin sequence and re-issuing the input instruction. In most situations this latency is acceptable, although it results in a response time which is longer than the virtual cycle time because of the time for the re-issued instruction to pass through the pipeline.

To enable the virtual processor to perform one input or output per virtual cycle, a *fast-mode* is provided. When a thread is in fast-mode, it is not de-scheduled when an instruction can not complete; instead the instruction is re-issued until it completes.

Events and interrupts are slightly different from normal input and output, because a vector must also be supplied and the target instruction fetched before execution can proceed. However, the same ready request system is used. The result will be to make the thread runnable but with an empty instruction buffer.

A variation on the *fetch no-op* is the *event no-op*; this is used to access the resource which generated the event (or interrupt) using the thread identifier; the resource can then supply the appropriate vector in time for it to be used for instruction fetch during the event no-op memory access stage. This means that at most one virtual cycle is used to process the vector, so there will be at most two virtual cycles before instruction issue following an event or interrupt.

The XCORE scheduler therefore allows threads to be treated as virtual processors with performance predicted by tools. There is no possibility that the performance can be reduced below these predicted levels when virtual processors are combined.

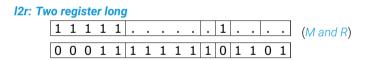

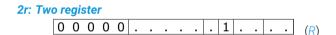

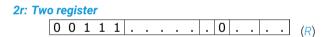

#### 5.2 Single and Dual Issue

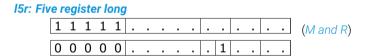

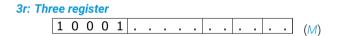

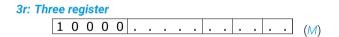

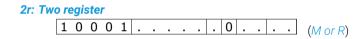

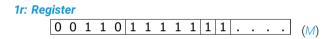

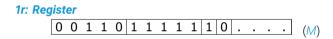

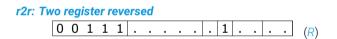

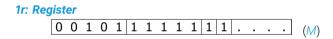

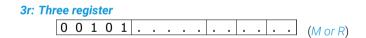

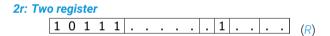

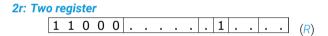

An XS3 pipeline has two *lanes*: the memory lane can execute all memory instructions, branches, and basic arithmetic, and the resource lane can execute all resource instructions and basic arithmetic. Each thread can chose to execute in *dual issue mode*, in which case the processor will execute two 16-bit instructions or a single 32-bit instruction in a

single thread cycle. In dual issue mode, all instructions must be aligned: 32-bit instructions must be 32-bit aligned and pairs of 16-bit instructions must be aligned on a 32-bit boundary. The program counter is always aligned to a 32-bit boundary and points to an issue slot rather than to an individual instruction. The 16 bit value stored at addresses 4n+2 and 4n+3 encodes an instruction for the memory lane. The 16-bit value stored at at addresses 4n+0 and 4n+1 encodes an instruction for the resource lane. Long instructions are stored in a word at addresses 4n+0...4n+3.

Where two instructions are executed simultaneously, any destination operands should be disjoint. If they are not disjoint, an exception will be raised.

When the resource lane stalls a thread, the other lane will be stalled also. This is normally not observable, except when an interrupt or an exception is raised. On an interrupt or exception, no registers will be overwritten, and the PC will point to the instruction to be reexecuted.

If an instruction in one of the two lanes causes an exception, then this exception is reported. If the other lane is executing an instruction then this second instruction is aborted. If the instructions in both lanes cause an exception, then only one exception is reported, and both instructions are aborted, but any memory store which is in progress will complete. On an exception, the savedPC value is set to the instruction that caused the exception.

A single bit in the status register, DI, enables dual-issue. If this bit is not set, then instructions flow through one lane at a time, and mis-aligned 32-bit instructions are allowed. The dual-issue-bit is set and cleared on a per function basis. The bit is saved in the lowest bit of LR when a function call is taken. It is restored on a RETSP instruction. The dual-issue-bit is set on executing a DUALENTSP x instruction, and cleared on executing an ENTSP x instruction. This enables functions to be dual or single issue.

#### 5.3 High priority threads

Threads can be set to be *high priority*. If no high priority threads are runnable, then a low priority thread will be scheduled if one is runnable. If high priority threads are runnable, then they will be scheduled, but at least one low priority thread will be executed on every iteration of the high priority queue. This means that all threads are always guaranteed progress.

Threads start as low-priority and only threads that require a very short turn around time or maximum throughput will be high priority.

### 6 Instruction Set Notation and Definitions

In the following description

| Identifier | Meaning                                                                           |

|------------|-----------------------------------------------------------------------------------|

| Bpw        | is the number of bytes in a word                                                  |

| bpw        | is the number of bits in a word                                                   |

| тет        | represents the memory                                                             |

| рс         | represents the program counter                                                    |

| sr         | represents the status register                                                    |

| sp         | represents the stack pointer                                                      |

| dp         | represents the data pointer                                                       |

| ср         | represents the constant pool pointer                                              |

| lr         | represents the link register                                                      |

| r0 r11     | represent specific operand registers                                              |

| X          | (a single small letter) represents one of r0 r11                                  |

| Х          | (a single large letter) represents one of r0 r11, sp, dp, cp, lr                  |

| U_S        | is a small unsigned source operand in the range 0 11                              |

| bitp       | is one of <i>bpw</i> , 1, 2, 3, 4, 5, 6, 7, 8, 16, 24, 32 encoded as a <i>u_s</i> |

| u16        | is a 16-bit source operand in the range 0 65535                                   |

| u20        | is a 20-bit source operand in the range 0 1048575                                 |

| iw         | is the issue-width in bytes, 2 (for single issue) or 4 (for dual issue)           |

Note that when the program counter (*pc*) is used by an instruction, it is always pointing to the next instruction. Instructions that access the location of the current instruction use  $pc_old$ .

The operators used in this manual are:

| Opera-<br>tor      | Meaning                                                                                                                                   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|                    | logical or                                                                                                                                |

| 1                  | bitwise or                                                                                                                                |

| &&                 | logical and                                                                                                                               |

| &                  | bitwise and                                                                                                                               |

| +, -, x , //,<br>% | arithmetic operations; full precision unsigned integer, unless specified as <i>signed</i>                                                 |

| 2^n                | integer power                                                                                                                             |

| <- r               | assignment of <i>r</i> to <i>l</i> ; if <i>r</i> has more bits than <i>l</i> , then the most significant bits of <i>r</i> will be ignored |

| !                  | logical not                                                                                                                               |

| ~                  | bitwise not                                                                                                                               |

| @                  | bitwise xor                                                                                                                               |

| mem[x]             | An entity at memory address x                                                                                                             |

| y[bit x]           | A single bit of y                                                                                                                         |

| y[bits<br>xz]      | A slice of y comprising x-z+1 bits; $x \ge z$                                                                                             |

| x:y                | Concatenates x and y, ie, x « bpw   y                                                                                                     |

| forall x<br>in y   | for each value x in the set y                                                                                                             |

Some useful functions are

- ▶ *zext(x, n) = x & (2^n 1)*: zero extend

- ▶ sext(x, n) = -(2^(n-1) & x) / x: sign extend

#### 6.1 Instruction Prefixes

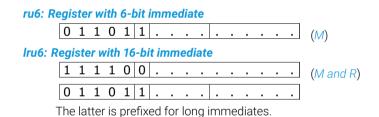

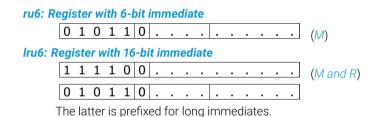

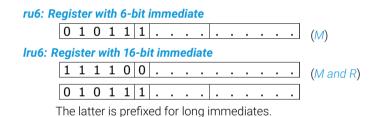

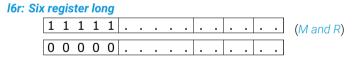

If the most significant 10 bits of a u16 or u20 instruction operand are non-zero, a 16-bit prefix (PFIX) preceding the instruction is used to encode them. The least significant bits are encoded within the instruction itself.

A different kind of 16-bit prefix (EOPR) is used to encode instructions with more than three operands, or to encode the less common instructions.

#### 7 Data Access

#### 7.1 Access to words

The data access instructions fall into several groups. One of these provides access via the stack pointer.:

Another is similar, but provides access via the data pointer.:

Access to constants and program addresses is provided by instructions which either load values directly or load them from the constant pool.:

Access to data structures is provided by instructions which use any of the operand registers as a base address, and combine this with a scaled offset. In the case of word accesses, the operand may be a small constant or another operand register, and the instructions are as follows:

| STWI<br>LDAWFI | d < mem[b + u_s x Bpw]<br>mem[b + u_s x Bpw] <- s<br>d < b + u_s x Bpw<br>d < b - u_s x Bpw | load word<br>store word<br>load address of word forward<br>load address of word backward |

|----------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| LDW            | d <- mem[b + i x Bpw]                                                                       | load word                                                                                |

| STW            | mem[b + i x Bpw] <- s                                                                       | store word                                                                               |

| LDAWF          | d <- b + i x Bpw                                                                            | load address of word forward                                                             |

| LDAWB          | d <- b - i x Bpw                                                                            | load address of word backward                                                            |

#### 7.2 Access to sub-words

In the case of access to 16-bit quantities, the base address is combined with a scaled operand, which must be an operand register. The least significant bit of the resulting address must be zero. The 16-bit item is loaded and sign extended into a word:

|        |                     | load 16-bit signed item              |

|--------|---------------------|--------------------------------------|

| ST16   | mem[b + i x 2] <- s | store 16-bit item                    |

| LDA16F | d <- b + i x 2      | load address of 16-bit item forward  |

| LDA16B | d <- b - i x 2      | load address of 16-bit item backward |

In the case of access to 8-bit quantities, the base address is combined with an unscaled operand, which must be an operand register. The 8-bit item is loaded and zero extended into a word.:

| LD8U | d <- zext(mem[b + i], 8) | load byte unsigned |

|------|--------------------------|--------------------|

| ST8  | mem[b + i] <- s          | store byte         |

Access to part words, including bit-fields, is provided by a small set of instructions which are used in conjunction with the shift and bitwise operations described below. These instructions provide for mask generation of any length up to 32 bits, sign extension and zero-extension from any bit position, and clearing fields within words prior to insertion of new values.:

| MKMSK  | d <- 2^s - 1       | make mask             |

|--------|--------------------|-----------------------|

| MKMSKI | d <- 2^bitp - 1    | make mask immediate   |

|        | d <- sext(d, s)    | sign extend           |

|        | d <- sext(d, bitp) | sign extend immediate |

|        | d <- zext(d, s)    | zero extend           |

| ZEXTI  | d <- zext(d, bitp) | zero extend immediate |

| ANDNOT | d <- d && ~ s      | and not (clear field) |

The SEXTI and ZEXTI instructions can also be used in conjunction with the LD16S and LD8U instructions to load unsigned 16-bit and signed 8-bit values.

#### 7.3 Access to double words

Pairs of words can be accessed in a single instruction. This requires the address to be aligned on a two-word boundary; it must be a multiple of Bpw x 2. For store operations two destination registers must be specified, for load operations two source registers must be specified.:

Note that the stack pointer must be double word aligned if double loads and double stores are used. The LDDSP and STDSP instructions can be used for saving context efficiently.

### 8 Expression Evaluation

```

ADDI

d <- 1 + u s

add immediate

d <- 1 + r

d <- 1 - u s

ADD

add

SUBI

subtract immediate

d <- 1 - r

SUB

subtract

NEG

d <- - s

negate

d <- l = u_s

d <- l = r

d <- l < r

EQI

equal immediate

EQ

equal

less than unsigned

I SU

LSS

d <- 1 <_sgn r

less than signed

AND

d <- 1 & r

and

d <- 1 | r

d <- 1 @ r

OR

or

XOR

exclusive or

XOR4

d <- 1 @ r @ s @ t

exclusive or

NOT

d <- ~ s

not

SHLI

d <- 1 << bitp

logical shift left immediate

logical shift left

logical shift left

logical shift right immediate

logical shift right

arithmetic shift right immediate

d <- l << r

d <- l >> bitp

SHI

SHRI

SHR1

d <- 1 >> Ditp

SHR

d <- 1 >> r

ASHRI

d <- 1 >>_sgn bitp

ASHR

d <- 1 >>_sgn r

arithmetic shift right

d <- 1 x r

d <- 1 // r

d <- 1 //_sgn r

d <- 1 % r

d <- 1 %_sgn r

multiply

MUI

divide unsigned

DIVU

DIVS

divide signed

remainder unsigned

remainder signed

REMU

REMS

NOP

no operation

```

The shift instructions SHL, SHR, and ASHR interpret their third operand (the shift distance) as a signed number, and accept negative operands. When presented with a negative shift-value:

- SHR will perform a shift left with the negative value.

- ▶ ASHR will perform a shift left with the negative value.

- SHL will perform an arithmetic shift right with the negative value.

Note that for positive shifts, these instructions are backwards compatible with the XS2 architecture.

```

BITREVd : for x in bpwd[bit ix] = s[bit bpw-ix-1]bit reverseBYTEREVd : for ix in bpw/8d[byte ix] = s[byte Bpw-ix-1]byte reverseCLZd <- 32,</td>if s = 0count leading

count leading zeros

lowest x : s[bpw-1-x] = 1,

otherwise

CLS

d <- 32.

if s = 0

count leading signbits

32.

if s =

lowest x : s[bpw-1-x] != s[bpw-1], otherwise

7TP

w = 2^{\wedge}s

zip double word

z = d[bpw-1..bpw-w-1]:

e[bpw-1..bpw-w-1]:

d[bpw-w-1..bpw-2 x w-1]:

e[bpw-w-1..bpw-2 x w-1]: ... :

d[w-1..0]:

e[w-1..0]:

(continues on next page)

```

(continued from previous page)

```

d <- z[2 bpw-1..bpw]

e <- z[bpw-1..0]

UNZIP w = 2^s unzip double word

z = d:e

d <- z[2 x bpw-1..2 x bpw-w-1]:

z[2 x bpw-2w-1..2 x bpw-3w-1]:...:

z[2 x bpw-w-1..2 x bpw-2w-1]:

z[2 x bpw-3w-1..2 x bpw-2w-1]:

z[2 x bpw-3w-1..2 x bpw-4w-1]:...:

z[w-1..0]

```

## 9 Branching, Jumping and Calling

The branch instructions include conditional and unconditional relative branches. A branch using the address in a register is provided; a relative branch which adds a scaled register operand to the program counter is provided to support jump tables:

| BRFT<br>BRFF | if c then pc <- pc + u16 x iw<br>if !c then pc <- pc + u16 x iw | branch relative forward true<br>branch relative forward false                   |

|--------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------|

| BRBT         | if c then pc <- pc - u16 x iw                                   | branch relative backward true                                                   |

| BRBF         | if !c then pc <- pc - u16 x iw                                  | branch relative backward false                                                  |

| BRFU<br>BRBU | pc <- pc + u16 x iw                                             | branch relative forward unconditional<br>branch relative backward unconditional |

| BRU          | pc <- pc - u16 x iw<br>pc <- pc + s x iw                        | branch relative backward unconditional<br>branch relative unconditional via reg |

| BAU          | pc <- s                                                         | branch absolute unconditional via reg                                           |

In some cases, the calling instructions described below can be used to optimise branches; as they overwrite the link register they are not suitable for use in leaf procedures which do not save the link register.

The procedure calling instructions include relative calls, calls via the constant pool, indexed calls via a dedicated register (r11) and calls via a register. Most calls within a single program module can be encoded in a single instruction; inter-module calling requires at most two instructions.:

| BLRF  | lr <- pc    sr[bit di];<br>pc <- pc + u20 x iw        | branch and link relative forward      |

|-------|-------------------------------------------------------|---------------------------------------|

| BLRB  | lr <- pc    sr[bit di];<br>pc <- pc - u20 x iw        | branch and link relative backward     |

| BLACP | lr <- pc    sr[bit di];<br>pc <- mem[cp + u20 x Bpw]  | branch and link absolute via CP       |

| BLAT  | lr <- pc    sr[bit di];<br>pc <- mem[r11 + u16 x Bpw] | branch and link absolute via table    |

| BLA   | lr <- pc    sr[bit di]<br>pc <- s                     | branch and link absolute via register |

Notice that control transfers which do not affect the link (required for tail calls to procedures) can be performed using one of the LDWCP, LDWCPL, LDAPF or LDAPB instructions followed by BAU r11.

Calling may require modification of the stack. Typically, the stack is extended on procedure entry and contracted on exit. The instructions to support this are shown below:

Functions can be made that can be entered in either single or dual issue:

- ► A single issue function must start with either a 32-bit aligned, long ENTSP instruction, or a short 32-bit aligned instruction that is paired with a dual-issuable instruction. This enables the function to be called from both single and dual issue contexts.

- A DUALENTSP instruction must either be a long instruction that is 32-bit aligned, or it must be a short DUALENTSP that is stored in the third and fourth byte of the word, together with an instruction that can be executed in the resource lane.

A short DUALENTSP executed in single issue stored in the lower 16-bits of a word will raise an exception in the following instruction, since the PC will be misaligned.

Notice that the stack and data area can be contracted using the LDAWSP and LDAWDP instructions.

In some situations, it is necessary to change to a new stack pointer, data pointer or pool pointer on entry to a procedure. Saving or restoring any of the existing pointers can be done using normal STWS, STWD, LDWS or LDWD instructions; loading them from another register can be optimised using the following instructions.:

| SETSP | sp <- s | set stack pointer |

|-------|---------|-------------------|

| SETDP | dp <- s | set data pointer  |

| SETCP | cp <- s | set pool pointer  |

## 10 Resources and the Thread Scheduler

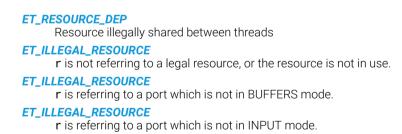

Each XCORE manages a number of different types of *resource*. These include threads, synchronisers, channel ends, timers and locks. For each type of resource a set of available items is maintained. The names of these sets are used to identify the type of resource to be allocated by the GETR (get resource) instruction. When the resource is no longer needed, it can be released for subsequent use by a FREER (free resource) instruction.:

| GETR  | r <- first res in setof(us): !inuse(res)<br>inuse(r) <- true | get resource  |

|-------|--------------------------------------------------------------|---------------|

| FREER | inuse(r) <- false                                            | free resource |

In the above setof(r) returns the set corresponding to the source operand of r. The resources are:

| resource name | set           | use                    |

|---------------|---------------|------------------------|

| THREAD        | threads       | concurrent execution   |

| SYNC          | synchronisers | thread synchronisation |

| CHANEND       | channel ends  | thread communication   |

| TIMER         | timers        | timing                 |

| LOCK          | locks         | mutual exclusion       |

Some resources have associated control *modes* which are set using the SETC instruction.:

SETC control(r) <- u16 set resource control

Many of the mode settings are defined only for a specific kind of resource and are described in the appropriate section; the ones which are used for several different kinds of resource are:

| mode      | effect                         |

|-----------|--------------------------------|

| OFF       | resource off                   |

| ON        | resource on                    |

| START     | resource active                |

| STOP      | resource inactive              |

| EVENT     | resource will cause events     |

| INTERRUPT | resource will raise interrupts |

Execution of instructions from each thread is managed by the *thread scheduler*. This maintains a set of runnable threads, \$run\$, from which it takes instructions in turn. When a thread is unable to continue, it is *paused* by removing it from the \$run\$ set. The reason for this may be any of the following.

- ▶ Its registers are being initialised prior to it being able to run.

- ▶ It is waiting to synchronise with another thread before continuing.

- ▶ It is waiting to synchronise with another thread and terminate (a join).

- It has attempted an input from a channel which has no data available, or a port which is not ready, or a timer which has not reached a specified time.

- ▶ It has attempted an output to a channel or a port which has no room for the data.

- It has executed an instruction causing it to wait for one of a number of events or interrupts which may be generated when channels, ports or timers become ready for input.

The thread scheduler manages the threads, thread synchronisation and timing (using the synchronisers and timers). It is directly coupled to resources such as the ports and channels so as to minimise the delay when a thread becomes runnable as a result of a communication or input-output.

## **11** Concurrency and Thread Synchronisation

A thread can initiate execution on one or more newly allocated threads, and can subsequently synchronise with them to exchange data or to ensure that all threads have completed before continuing. Thread synchronisation is performed using hardware *synchronisers*, and threads using a synchroniser will move between running states and paused states. When a thread is first created, its status register is initialised as follows:

| <pre>sr[bit eeble]</pre>   | <-  | 0 |                      |

|----------------------------|-----|---|----------------------|

| <pre>sr[bit ieble]</pre>   | < - | 0 |                      |

| <pre>sr[bit inenb]</pre>   | < - | 0 |                      |

| <pre>sr[bit inint]</pre>   | < - | 0 |                      |

| sr[bit hipri]              | <-  | 0 |                      |

| sr[bit fast]               | < - | 0 |                      |

| sr[bit kedi]               | < - | 0 |                      |

| <pre>sr[bit waiting]</pre> | < - | 1 | the thread is paused |

| sr[bit di]                 | < - | 0 |                      |

The access registers of the newly created thread can be initialised using the following instructions.:

| TINITPC | pc(t) <- s | set thread pc    |

|---------|------------|------------------|

| TINITSP | sp(t) <- s | set thread stack |

| TINITDP | dp(t) <- s | set thread data  |

| TINITCP | cp(t) <- s | set thread pool  |

| TINITLR | lr(t) <- s | set thread link  |

|         |            |                  |

These instructions can only be used when the thread is paused. The TINITLR instruction is intended primarily to support debugging. On thread initialisation, the PC must be initialised. DP, SP, and CP will retain their value on freeing and allocating threads, so they may not have to be reinitialised.

Data can be transferred between the operand registers of two threads using TSETR and TSETMR instructions, which can be used even when the destination thread is running.:

To start a *synchronised* slave thread a master must first acquire a synchroniser. This is done using a GETR SYNC instruction. If there is a synchroniser available its resource ID is returned, otherwise the invalid resource ID is returned. The GETST instruction is then used to get a synchronised thread. It is passed the synchroniser ID and if there is a free thread it will be allocated, attached to the synchroniser and its ID returned, otherwise the invalid resource ID is returned.

The master thread can repeat this process to create a group of threads which will all synchronise together. To start the slave threads the master executes an MSYNC instruction using the synchroniser ID.:

```

GETST d <- first res in setof(threads): !inuse(res) get synchronised thread

inuse(d) <- true

spaused <- spaused union {d};

slaves(s) <- slaves(s) union {d}

mstr(s) <- tid

MSYNC if (slaves(s) setminus spaused = {}) master synchronise

then

spaused <- spaused setminus slaves(s)

else

mpaused <- mpaused union {tid};

msyn(s) <- true</pre>

```

The group of threads can synchronise at any point by the slaves executing the SSYNC and the master the MSYNC. Once all the threads have synchronised they are unpaused and continue executing from the next instruction. The processor maintains a set of paused master threads mpaused and a set of paused slave threads spaused from which it derives the set of runnable threads **run**

```

run = {thread in threads : inuse(thread)} setminus (spaused union mpaused)

```

Each synchroniser also maintains a record msyn(s) of whether its master has reached a synchronisation point.:

```

SSYNC if (slaves(syn(tid)) setminus spaused = {tid}) && msyn(syn(tid)) slave

then

if mjoin(syn(tid))

then

for t in slaves(syn(tid)) : inuse(t) <- false;

mjoin(syn(tid)) <- false

else

spaused <- spaused setminus slaves(syn(tid));

mpaused <- mpaused setminus {mstr(syn(tid))};

msyn(syn(tid)) <- false

else

spaused <- spaused union {tid}</pre>

```

To terminate all of the slaves and allow the master to continue the master executes an MJOIN instruction instead of an MSYNC. When this happens, the slave threads are all freed and the master continues.:

```

MJOIN if (slaves(s) = spaused) master join

then

for t in slaves(s) : inuse(t) <- false;

mjoin(syn(tid)) <- false

else

mpaused <- mpaused union {tid};

mjoin(s) <- true;

msyn(s) <- true</pre>

```

A master thread can also create threads which can terminate themselves. This is done by the master executing a GETR THREAD instruction. This instruction returns either a thread ID if there is a free thread or the invalid resource ID. The unsynchronised thread can be initialised in the same way as a synchronised thread using the TINITPC, TINITSP, TINITDP, TINITCP, TINITLR and TSETR instructions.

The unsynchronised thread is then started by the master executing a TSTART instruction specifying the thread ID. Once the thread has completed its task it can terminate itself with the FREET instruction.:

TSTART spaused <- spaused setminus {tid} start thread FREET inuse(tid) <- false; free thread

The identifier of an executing thread can be accessed by the GETID instruction .:

GETID t <- tid get thread identifier

## **12** Communication

Communication between threads is performed using *channels*, which provide full-duplex data transfer between *channel ends*, whether the ends are both in the same XCORE, in different XCORES on the same chip or in XCORES on different chips. Channels carry messages constructed from data and control *tokens* between the two channel ends. The control tokens are used to encode communication protocols. Although most control tokens are available for software use, a number are reserved for encoding the protocol used by the interconnect hardware, and can not be sent and received using instructions.

A channel end can be used to generate events and interrupts when data becomes available as described below. This allows a thread to monitor several channels, ports or timers, only servicing those that are ready.

To communicate between two threads, two channel ends need to be allocated, one for each thread. This is done using the GETR c , CHANEND instruction. Each channel end has a *destination* register which holds the identifier of the destination channel end; this is initialised with the SETD instruction. It is also possible to use the identifier of a channel end to determine its destination channel end.:

The identifier of the channel end c1 is used to initialise the channel end for thread c2, and vice versa. Each thread can then use the identifier of its own channel end to transfer data and messages using output and input instructions.

The interconnect can be partitioned into several independent networks. This makes it possible, for example, to allocate channels carrying short control messages to one network whilst allocating channels carrying long data messages to another. There are instructions to allocate a channel to a network and to determine which network a channel is using.:

| SETN | c(net) <- s | set | network |

|------|-------------|-----|---------|

| GETN | d <- c(net) | get | network |

In the following, c <: s represents an output of s to channel c and c :> d represents an input from channel c into d.:

| OUTT<br>OUTCT<br>OUTCTI | c <: dtoken(s)<br>c <: ctoken(s)<br>c <: ctoken(us) | output token<br>output control token<br>output control token immediate |                          |

|-------------------------|-----------------------------------------------------|------------------------------------------------------------------------|--------------------------|

| INT                     | if hasctoken(c)<br>then trap                        | input token                                                            |                          |

|                         |                                                     |                                                                        | (continues on next page) |

(continued from previous page)

| INCT              | else c :> d<br>if hasctoken(c)<br>then c :> d<br>else trap      | input control token                                   |

|-------------------|-----------------------------------------------------------------|-------------------------------------------------------|

| СНКСТ             | if hasctoken(c)&&(s=token(c))<br>then skiptoken(c)<br>else trap | check control token                                   |

| CHKCTI            | if hasctoken(c)&&(s=token(c))<br>then skiptoken(c)<br>else trap | check control token immediate                         |

| OUT<br>IN         | c <: s<br>if containsctoken(c)<br>then trap<br>else c :> d      | output data word<br>input token                       |

| TESTCT<br>TESTWCT | d <- hasctoken(c)<br>d <- containsctoken(c)                     | test for control token<br>test word for control token |

The channel connection is established when the first output is executed. If the destination channel end is on another XCORE, this will cause the destination identifier to be sent through the interconnect, establishing a route for the subsequent data and control tokens. The connection is terminated when an END control token is sent. If a subsequent output is executed using the same channel end, the destination identifier will be used again to establish a new route which will again persist until another END control token is sent.

A destination channel end can be shared by any number of outputting threads; they are served in a round-robin manner. Once a connection has been established it will persist until an END is received; any other thread attempting to establish a connection will be queued. In the case of a shared channel end, the outputting thread will usually transmit the identifier of its channel end so that the inputting thread can use it to reply.

The OUT and IN instructions are used to transmit words of data through the channel; to transmit bytes of data the OUTT and INT instructions are used. Control tokens are sent using OUTCT or OUTCTI and received using INCT. To support efficient runtime checks that the type, length or structure of output data matches that expected by the inputer, CHKCT and CHKCTI instructions are provided. The CHKCT instruction inputs and discards a token provided that the input token matches its operand; otherwise it traps. The normal IN and INT instructions trap if they encounter a control token. To input a control token INCT is used; this traps if it encounters a data token.

The END control token is one of the 12 tokens which can be sent using OUTCTI and checked using CHKCTI. By following each message output with an OUTCTI *c*, END and each input with a CHKCTI *c*, END it is possible to check that the size of the message is the same as the size of the message expected by the inputting thread. To perform synchronised communication, the output message should be followed with (OUTCTI *c*, END; CHKCTI *c*, END) and the input with (CHKCTI *c*, END; OUTCTI *c*, END).

Another control token is PAUSE. Like END, this causes the route through the interconnect to be disconnected. However the PAUSE token is not delivered to the receiving thread. It is used by the outputting thread to break up long messages or streams, allowing the interconnect to be shared efficiently. The remaining control tokens are used for runtime checking and for signalling the type of message being received; they have no effect on the interconnect. Note that in addition to END and PAUSE, ten of these can be efficiently handled using OUTCTI and CHKCTI.

A control token takes up a single byte of storage in the channel. On the receiving end the software can test whether the next token is a control token using the TESTCT instruction, which waits until at least one token is available. It is also possible to test whether the next word contains a control token using the TESTWCT instruction. This waits until a whole word of data tokens has been received (in which case it returns 0) or until a control token

has been received (in which case it returns the byte position after the position of the byte containing the control token).

Channel ends have a buffer able to hold sufficient tokens to allow at least one word to be buffered. If an output instruction is executed when the channel is too full to take the data then the thread which executed the instruction is paused. It is restarted when there is enough room in the channel for the instruction to successfully complete. Likewise, when an input instruction is executed and there is not enough data available then the thread is paused and will be restarted when enough data becomes available.

Note that when sending long messages to a shared channel, the sender should send a short request and then wait for a reply before proceeding as this will minimise interconnect congestion caused by delays in accepting the message.

When a channel end \$c\$ is no longer required, it can be freed using a FREER \$c\$ instruction. Otherwise it can be used for another message.

It is sometimes necessary to determine the identifier of the destination channel end c2stored in channel end c1. For example, this enables a thread to transmit the identifier of a destination channel end it has been using to a thread on another processor. This can be done using the GETD instruction. It is also useful to be able to determine quickly whether a destination channel end c2 stored in channel end c1 is on the same processor as c1; this makes it possible to optimise communication of large data structures where the two communicating threads are executed by the same processor.

TESTLCL d <- islocal(c) test destination local

## 13 Locks

Mutual exclusion between a number of threads can be performed using *locks*. A lock is allocated using a GETR \$I\$, LOCK instruction. The lock is initially *free*. It can be *claimed* using an IN instruction and freed using an OUT instruction.

When a thread executes an IN on a lock which is already claimed, it is paused and placed in a queue waiting for the lock. Whenever a lock is freed by an OUT instruction and the lock's queue is not empty, the next thread in the queue is unpaused; it will then succeed in claiming the lock.

When inputting from a lock, the IN instruction always returns the lock identifier, so the same register can be used as both source and destination operand. When outputting to a lock, the data operand of the OUT instruction is ignored.

When the lock is no longer needed, it can be freed using a FREER / instruction.

## 14 Timers

Each XCORE executes instructions at a speed determined by its own clock input. In addition, it provides a reference clock output which ticks at a standard frequency of 100MHz. A set of programmable timers is provided and all of these can be used by threads to provide timed program execution relative to the reference clock.

#### 14.1 Using timers

The processor has a set of timers that can be used to wait for a time. The current time can be input from any timer, or it can be obtained by using GETTIME:

GETTIME d <- current time get current time

Each timer can be used by a thread to read its current time or to wait until a specified time. A timer is allocated using the GETR \$t\$, TIMER instruction. It can be configured using the SETC instruction; the only two modes which can be set are UNCOND and AFTER.

| mode            | effect                                                                                                                  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| UNCOND<br>AFTER | timer <i>always</i> ready; inputs complete immediately timer ready when its current time is <i>after</i> its DATA value |

In unconditional mode, an IN instruction reads the current value of the timer. In AFTER mode, the IN instruction waits until the value of its current time is after (later than) the value in its DATA register. The value can be set using a SETD instruction. Timers can also be used to generate events as described below.

A set of programmable clocks is also provided and each can be used to produce a clock output to control the action of one or more ports and their associated port timers. The ports are connected to a clock using the SETCLK instruction.:

SETCLK clock(d) <- s set clock source

Each port p which is to be clocked from a clock c can be connected to it by executing a SETCLK p, c instruction.

Each clock can use a one bit port as its clock source. A clock *c* which is to use a port *p* as its clock source can be connected to it by executing a SETCLK *p*, *c* instruction. Alternatively, a clock may use the reference clock as its clock source (by SETCLK *p*, REF). In either case the clock can be configured to divide the frequency using an 8-bit divider. When this is set to 0, the clock passes directly to the output. The falling edge of the clock is used to perform the division. Hence a setting of 1 will result in an output from the clock which changes each falling edge of the input, halving the input frequency *f*; and a setting of *n* will produce an output frequency of *f*/2*n*. The division factor is set using the SETD instruction. The lowest eight bits of the operand are used and the rest ignored.

To ensure that the timers in the ports which are attached to the same clock all record the same time, the clock should be started using a SETC *c*, START instruction *after* the ports have all been attached to the clock. All of the clocks are initially stopped and a clock can be stopped by a SETC *c*, STOP instruction.

The data output on the pins of an output port changes state synchronously with the port clock. If several output ports are driven from the same clock, they will appear to operate as a single output port, provided that the processor is able to supply new data to all of them during each clock cycle. Similarly, the data input by an input port from the port pins is sampled synchronously with the port clock. If several input ports are driven from the same clock they will appear to operate as a single input port provided that the processor is able to take the data from all of them during each clock cycle.

The use of clocked ports therefore decouples the internal timing of input and output program execution from the operation of synchronous input and output interfaces.

## 15 Ports, Input and Output

Ports are interfaces to physical pins. A port can be used for *input* or *output*. It can use the reference clock as its port clock or it can use one of the programmable clocks. Transfers to and from the pins can be *synchronised* with the execution of input and output instructions, or the port can be configured to *buffer* the transfers and to convert automatically between serial and parallel form. Ports can also be *timed* to provide precise

timing of values appearing on output pins or taken from input pins. When inputting, a *condition* can be used to delay the input until the data in the port meets the condition. When the condition is met the captured data is *time stamped* with the time at which it was captured.

The port clock input is initially the reference clock. It can be changed using the SETCLK instruction with a clock ID as the clock operand. This port clock drives the port timer and can also be used to determine when data is taken from or presented to the pins.

A port can be used to generate events and interrupts when input data becomes available as described below. This allows a thread to monitor several ports, channels or timers, only servicing those that are ready.

#### 15.1 Input and Output

Each port has a *transfer register*. The input and output instructions used for channels, IN and OUT, can also be used to transfer data to and from a port transfer register. The IN instruction zero-extends the contents of a port transfer register and transfers the result to an operand register. The OUT instruction transfers the least significant bits from an operand register to a port transfer register.

Two further instructions, INSHR and OUTSHR, optimise the transfer of data. The INSHR instruction shifts the contents of its destination register right, filling the left-most bits with the data transferred from the port. The OUTSHR instruction transfers the least significant bits of data from its source register to the port and shifts the contents of the source register right.:

| OUTSHR | p <: s[0trwidth(p)];<br>s <- s >> trwidth(p)           | output to port<br><b>and</b> shift |

|--------|--------------------------------------------------------|------------------------------------|

| INSHR  | s <- s >> trwidth(p);<br>p :> s[(bpw-trwidth(p))bpw-1] | shift and<br>input from port       |

The transfer register is accessed by the processor; it is also accessed by the port when data is moved to or from the pins. When the processor writes data into the transfer register it *fills* the transfer register; when the processor takes data from the transfer register it *empties* the transfer register.

#### 15.2 Port Configuration

A port is initially OFF with its pins in a high impedance state. Before it is used, it must be configured to determine the way it interacts with its pins, and set ON, which also has the effect of starting the port. The port can subsequently be stopped and started using SETC \$p\$, STOP and SETC \$p\$, START; between these the port configuration can be changed.

The port configuration is done using the SETC instruction which is used to define several independent settings of the port. Each of these has a default mode and need only be configured if a different mode is needed. The effect of the SETC mode settings is described below. The **bold** entry in each setting is the default mode.

| mode              | effect                                                                                             |

|-------------------|----------------------------------------------------------------------------------------------------|

| NOREADY           | no ready signals are used                                                                          |

| HAND-<br>SHAKEN   | both ready input and ready output signals are used                                                 |

| STROBED           | one ready signal is used (output on master, input on slave)                                        |

| SYNCHRO-<br>NISED | processor synchronises with pins                                                                   |

| BUFFERED          | port buffers data between pins and processor                                                       |

| SLAVE             | port acts as a slave                                                                               |

| MASTER            | port acts as a master                                                                              |

| NOSDELAY          | input sample not delayed                                                                           |

| SDELAY            | input sample delayed half a clock period                                                           |

| DATAPORT          | port acts as normal                                                                                |

| CLOCK-<br>PORT    | the port outputs its source clock                                                                  |

| READY-<br>PORT    | the port outputs a ready signal                                                                    |

| DRIVE             | pins are driven both high and low                                                                  |

| PULL-<br>DOWN     | pins have a weak pull-down on input, on output pins are driven high only, high impedance otherwise |

| PULLUP            | pins have a weak pull-up on input, on output pins are driven low only high impedance otherwise     |

| KEEP              | pins keep their value on input                                                                     |

| NOINVERT          | data is not inverted                                                                               |

| INVERT            | data is inverted                                                                                   |

The DRIVE, PULLDOWN and PULLUP modes determine the way the pins are driven when outputting, and the way they are pulled when inputting. The CLOCKPORT, READYPORT and INVERT settings can only be used with 1-bit ports.

Initially, the port is ready for input. Subsequently, it may change to output data when an output instruction is executed; after outputting it may change back to inputting when an input instruction is executed.

It is sometimes useful to read the data on the pins when the port is outputting; this can be done using the PEEK instruction:

PEEK d <- pins(p) read port pins

#### 15.3 Configuring Ready and Clock Signals

A port can be configured to use ready input and ready output signals.

A port's ready input signal is input by an associated one-bit port. This association is made using the SETRDY instruction.:

SETRDY ready(p) <- s set source of port ready input

A port's ready output signal is output by another associated one-bit port. A one-bit port r which is to be used as a ready output must first be configured in READYPORT mode by

SETC *r*, READYPORT. This ready port *r* can then be associated with a port *p* by SETRDY *r*, *p*.

A one-bit port can be used to output a clock signal by setting it into CLOCKPORT mode; its clock source is set using the SETCLK instruction.

When a 1-bit port is configured to be in CLOCKPORT or READYPORT mode, the drive mode and invert mode are configurable as normal.

#### 15.4 NOREADY mode

If the port is in NOREADY mode, no ready signals are used and data is moved to and from the pins either asynchronously (at times determined by the execution of input and output instructions) or synchronously with the port clock, irrespective of whether the port is in MASTER or SLAVE mode.

At most one input or output is performed per cycle of the port clock.

#### 15.5 HANDSHAKEN mode

In HANDSHAKEN mode, ready signals are used to control when data is moved to or from a port's pins.

A port in MASTER HANDSHAKEN mode initiates an output cycle by moving data to the pins and asserting the ready output (request); it then waits for the ready input (reply) to be asserted. It initiates an input cycle by asserting the ready output (request) and waiting for the ready input (reply) to be asserted along with the data; it then takes the data.

A port in SLAVE HANDSHAKEN mode waits for the ready input (request) to be asserted. It performs an input cycle by taking the data and asserting the ready output (reply); it performs an output cycle by moving data to the pins and asserting the ready output (reply).

The ready signals accompany the data in each cycle of the port clock. The *falling edge* of the port clock initiates the set up of data or a change of port direction; the port timer also advances on this edge. On output, the data and the ready output will be valid on the *rising edge* of the port clock. On input, data and the ready input will be sampled on the rising edge of the port clock unless the port is configured as SDELAY, in which case they are sampled on the falling edge.

#### 15.6 STROBED mode

In STROBED mode only one ready signal is used and the port can be in MASTER or SLAVE mode. A MASTER port asserts its ready output and the slave has to keep up; a SLAVE port has to keep up with the ready input.

Note that a port in NOREADY mode behaves in the same way as a port in STROBED mode which is always ready.

#### **15.7 The Port Timer**

A port has a timer which can be used to cause the transfer of data to or from the pins to take place at a specified time. The time at which the transfer is to be performed is set using the SETPT (set port time) instruction. Timed ports are often used together with time-stamping as this allows precise control of response times.:

| SETPT | porttime(p) <- s  | set port time      |

|-------|-------------------|--------------------|

| CLRPT | clearporttime(p)  | clear port time    |

| GETTS | d <- timestamp(p) | get port timestamp |

The CLRPT instruction can be used to cancel a timed transfer.

The timestamp which is set when a port becomes ready for input can be read using the GETTS instruction.

#### 15.8 Conditions

A port has an associated *condition* which can be used to prevent the processor from taking input from the port when the condition is not met. The conditions are set using the SETC instruction. The value used for comparison in some of the conditions is held in the port data register, which can be set using the SETD instruction.

| mode | port ready condition                                |

|------|-----------------------------------------------------|

| NONE | no condition                                        |

| EQ   | value on pins equal to port data register value     |

| NEQ  | value on pins not equal to port data register value |

The simplest condition is NONE. The other conditions all involve comparing the value from the pins with the value in the port data register.

When the condition is met a timestamp is set and the port becomes ready for input.

When a port is used to generate an event, the data which satisfied the condition is held in the transfer register and the timestamp is set. The value returned by a subsequent input on the port is guaranteed to meet the condition and to correspond to the timestamp even if the value on the port has changed.

#### **15.9 Synchronised Transfers**

A port in SYNCHRONISED mode ensures that the signalling operation of the port pins is synchronised with the processor instruction execution.

When a SETPT instruction is used, the movement of data between the pins and the transfer register takes place when the current value of the port timer matches the time specified with the SETPT instruction.

If the port is used for output and the transfer register is full, the SETPT instruction will pause until the transfer register is empty. This ensures that the port time is not changed until the pending output has completed.

If a condition other than NONE is used the port will only be ready for input when the data in the transfer register matches the condition. If an input instruction is executed and the specified condition is not met, the thread executing the input will be paused until the condition is met; the thread then resumes and completes the input. The value of the port timer corresponding to the data in the transfer register when a port condition is met is recorded in the port timestamp register. The timestamp register is read at any time using the GETTS instruction.

#### 15.10 Buffered Transfers

A port in BUFFERED mode buffers the transfer of data between the processor and the pins through the use of a *shift register*, which is situated between the transfer register and the pins. A buffered port can be used to convert between parallel and serial form using its shift register. The number of bits in the transfer register and the shift register determines the width of the transfers (the *transfer width*) between the processor and the port; this is a multiple of the *port width* (the number of pins) and can be set by the SETTW instruction.:

SETTW width(p) <- s set port transfer width

For a 32-bit word-length, the transfer width is normally 32, 8, 4 or 1 bit.

Note that in contrast to a synchronised transfer, where the transfer width and the port width are equal, the transfer width of a buffered transfer can differ from the port width.

On input, the shift register is full when *n* values have been taken from the *p* pins, where  $n \times p$  is the transfer width; it will then be emptied to the transfer register ready for an input instruction. On output the shift register is filled from the transfer register and will be empty when *n* values have been moved to the *p* pins, where  $n \times p$  is the transfer width.

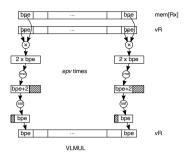

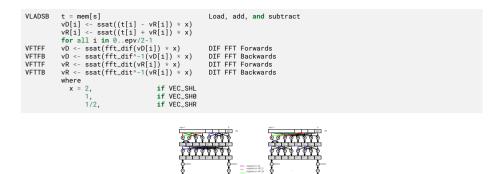

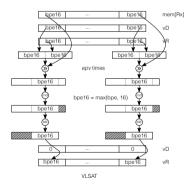

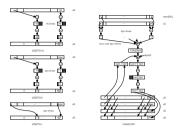

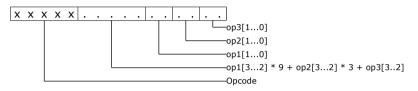

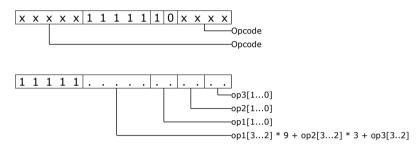

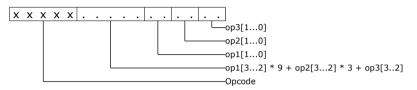

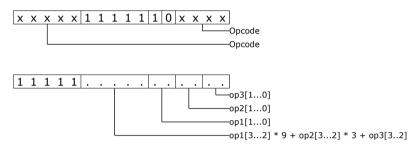

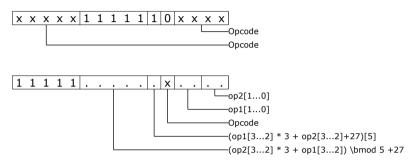

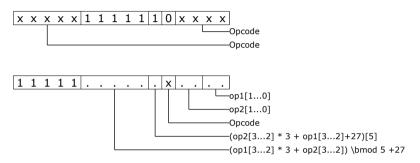

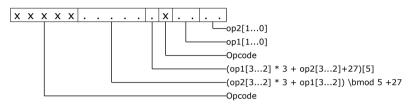

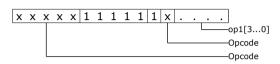

The port operates as follows: